Loading

Get Serdes Verilog Code

How it works

-

Open form follow the instructions

-

Easily sign the form with your finger

-

Send filled & signed form or save

How to fill out the Serdes Verilog Code online

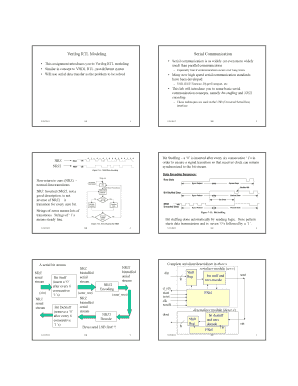

Filling out the Serdes Verilog Code form is crucial for understanding and implementing serial communication protocols in Verilog RTL modeling. This guide provides clear instructions to help users, regardless of their experience level, complete the form with confidence.

Follow the steps to successfully complete the Serdes Verilog Code form.

- Click ‘Get Form’ button to access the form and open it for editing.

- Begin by reviewing the components of the Serdes Verilog Code. Familiarize yourself with terms like serializer and deserializer, as well as encoding techniques such as NRZI and bit stuffing.

- In the serializer section, be attentive to the specifics of the module design. Include parameters such as the input and output interfaces, and ensure your code is synthesizeable.

- When filling in the deserializer section, follow the same principles as the serializer but focus on decoding aspects. Understand how to manage the transition of signal states to ensure data integrity.

- Make sure to incorporate testbench connections accurately, maintaining clear communication between your serializer and deserializer modules.

- After completing all the necessary fields, review your entries to ensure accuracy and completeness before finalizing.

- Once satisfied with your entries, save your changes. You can also download or print the form for your records or share it with your colleagues.

Start filling out the Serdes Verilog Code form online to elevate your digital document management experience.

To run System Verilog code, you need a simulator that supports this language. You can start by writing your code in your preferred text editor and saving it with a .sv extension. Next, use a tool like ModelSim or VCS to compile and execute your code. With the right tools, you can easily verify aspects of your Serdes Verilog Code, ensuring it behaves as expected.

Industry-leading security and compliance

US Legal Forms protects your data by complying with industry-specific security standards.

-

In businnes since 199725+ years providing professional legal documents.

-

Accredited businessGuarantees that a business meets BBB accreditation standards in the US and Canada.

-

Secured by BraintreeValidated Level 1 PCI DSS compliant payment gateway that accepts most major credit and debit card brands from across the globe.